题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

设计一个组合逻辑电路,要求当X=0时实现一位二进制数的...

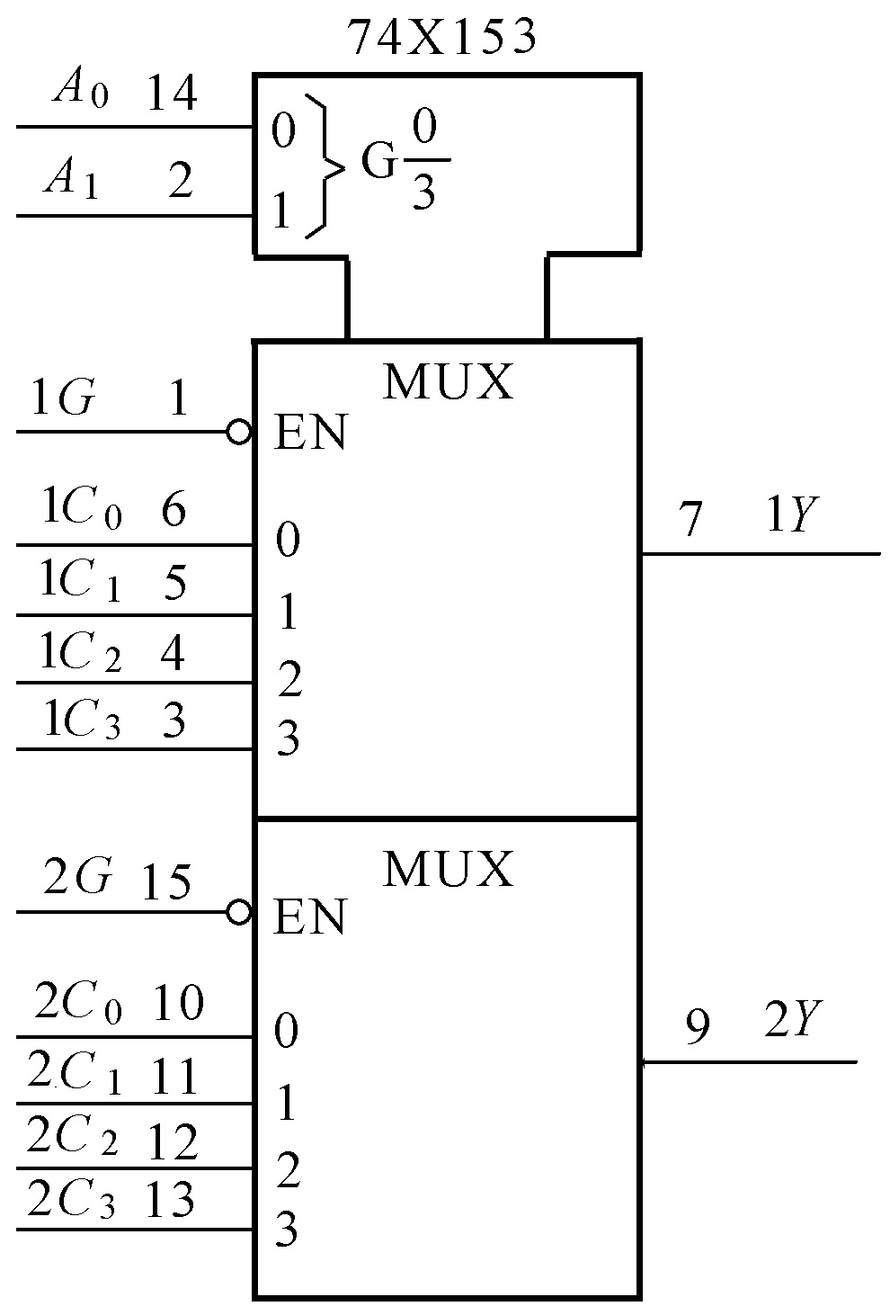

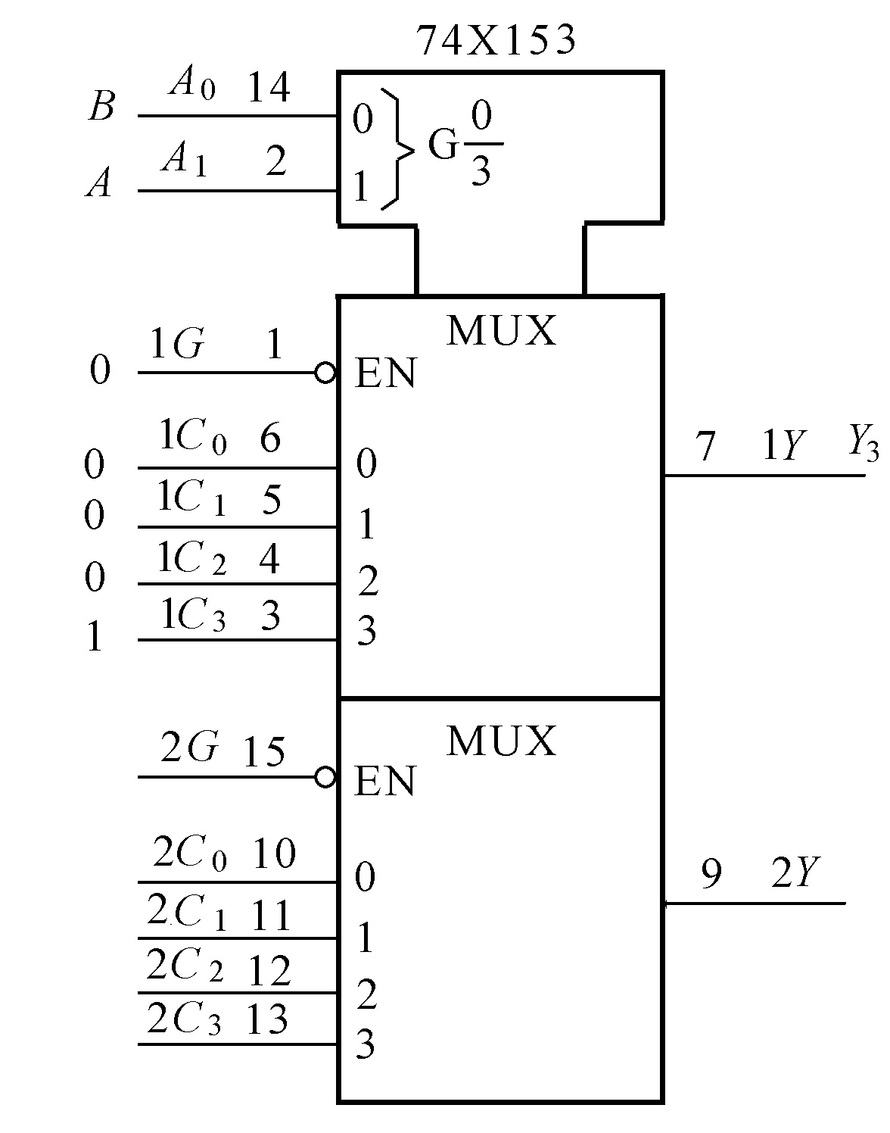

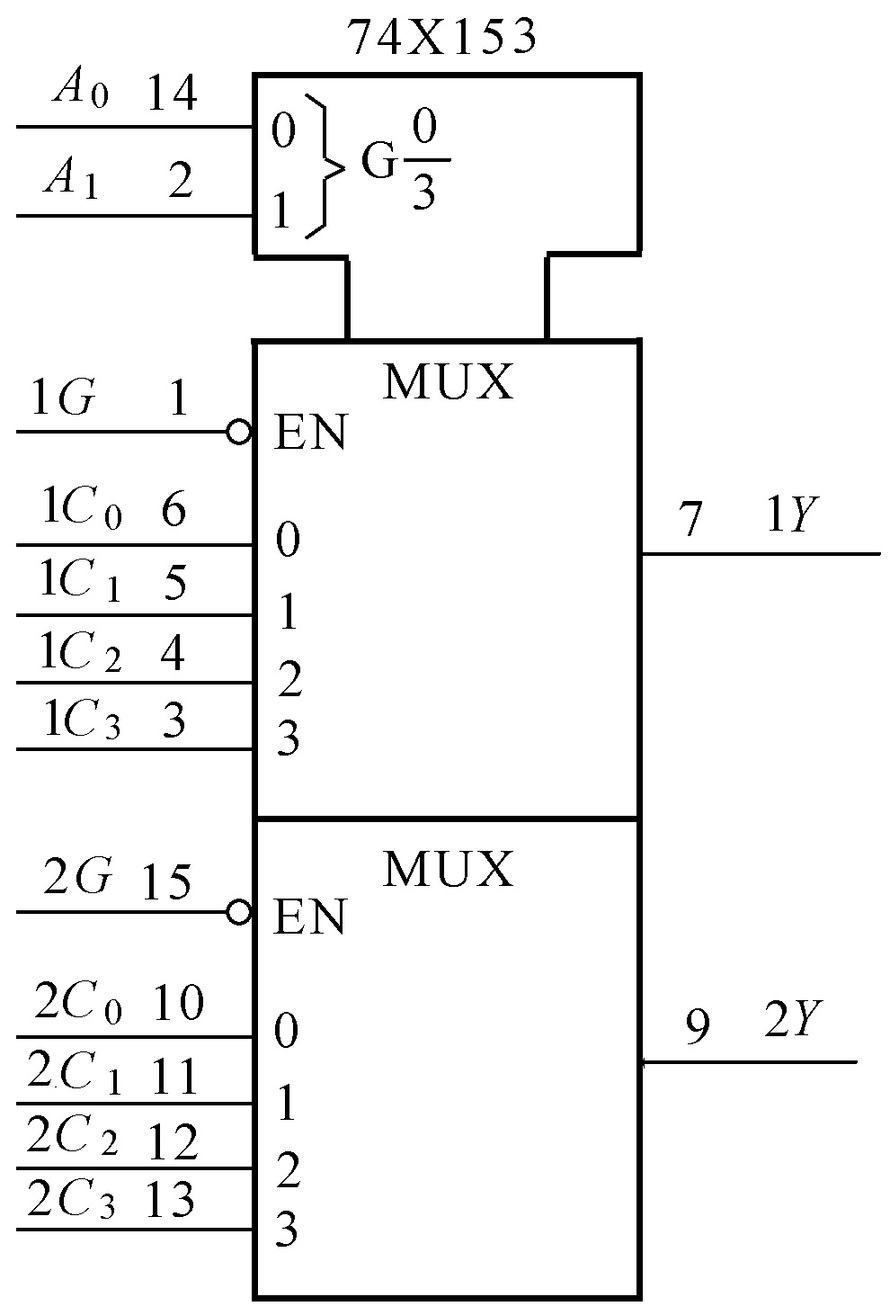

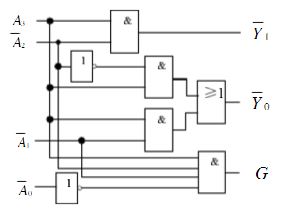

设计一个组合逻辑电路,要求当X=0时实现一位二进制数的半加功能,X=1时实现一位二进制数的半减功能。设计要求:(1)约定(2分);(2)写出真值表(4分);(3)卡诺图化简,写出最简与或式(2分);(4)用与非门实现,画出逻辑图(2分);(5)74X138芯片的国标符号如图所示,用74X138芯片实现该电路(5分)。(6)74X153芯片的国标符号如图所示,用74X153芯片实现该电路(5分)。

如搜索结果不匹配,请 联系老师 获取答案

如搜索结果不匹配,请 联系老师 获取答案

当G2G1=00时,对X2X1做加1运算;

当G2G1=00时,对X2X1做加1运算;1.jpg)

,

, 为二位二进制数,

为二位二进制数, 为最高位,

为最高位, 为四位二进制数,

为四位二进制数, 为最高位,则下列选项正确的是

为最高位,则下列选项正确的是