题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

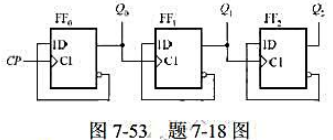

设计一个[图]进制计数器的电路至少需要[图]个触发器。...

设计一个![设计一个[图]进制计数器的电路至少需要[图]个触发器。...设计一个进制计数器的电路至少需要个触发器](http://static.jiandati.com/3607bdf-chaoxing2016-581.jpeg) 进制计数器的电路至少需要

进制计数器的电路至少需要![设计一个[图]进制计数器的电路至少需要[图]个触发器。...设计一个进制计数器的电路至少需要个触发器](http://static.jiandati.com/e279da8-chaoxing2016-40.jpeg) 个触发器。

个触发器。

如搜索结果不匹配,请 联系老师 获取答案

如搜索结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

设计一个![设计一个[图]进制计数器的电路至少需要[图]个触发器。...设计一个进制计数器的电路至少需要个触发器](http://static.jiandati.com/3607bdf-chaoxing2016-581.jpeg) 进制计数器的电路至少需要

进制计数器的电路至少需要![设计一个[图]进制计数器的电路至少需要[图]个触发器。...设计一个进制计数器的电路至少需要个触发器](http://static.jiandati.com/e279da8-chaoxing2016-40.jpeg) 个触发器。

个触发器。

如搜索结果不匹配,请 联系老师 获取答案

如搜索结果不匹配,请 联系老师 获取答案

更多“设计一个[图]进制计数器的电路至少需要[图]个触发器。...”相关的问题

更多“设计一个[图]进制计数器的电路至少需要[图]个触发器。...”相关的问题

第3题

第4题

当A3=0时,触发器E清零,计数器继续计数。

当A3=1时,触发器E置1,并检测A4,A4=0时,继续计数;A4=1时,触发器F置1,并停止计数,回到系统初始状态。

(1)试画出该系统的ASM图

(2)画出该系统控制单元的状态图,并用D触发器及必要的门电路设计控制单元

第5题

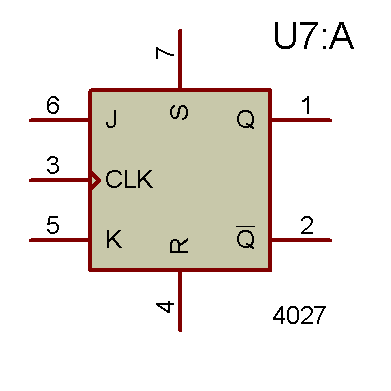

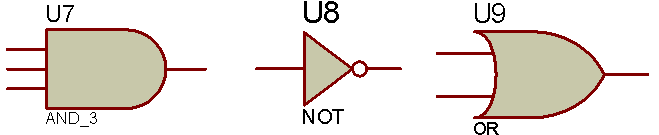

实验四:12进制计数器1、 设计说明 我们已经掌握的同步、异步触发器的相关知识,现在让我们利用JK触发器设计一个12进制计数器吧! 首先我们需要绘制12进制JK触发器设计的基本流程: 同步计数器的设计前我们首先需要熟悉J-K触发器的逻辑功能,掌握J-K触发器构成同步计数器方法,参考如下: 1.确定电路所需的触发器数目。 2.列出计数器的状态转换图。 3.根据状态转换图画出状态转换表。 4.根据状态转换表,写出J-K触发器的状态方程和驱动方程。 5.检查自启动性。 6.画出逻辑图。2、 选用仿真元件 2.1 JK触发器 2.2 常见门电路

2.2 常见门电路 三输入与门 非门 两输入或门3、 设计效果

三输入与门 非门 两输入或门3、 设计效果 12进制计数器评分标准 12进制计数器属于触发器课程的电路设计实验项目,该项目的完成要求具体如下: 1. 12进制计数器不能采用集成计数器芯片完成,只能用触发器设计,否则该项目不能计分。 2. 计数器的实现需要由四个触发器(同步或异步)设计而成,并通过数码管显示当前计数值,否则只能50%计入成绩。 3. 计数器可以设置一个清零键,该内容属于加分项。 4. 报告最后需加入本次实验的心得,字数不限,但切记雷同。 5. 报告请以“班级-学号-姓名”命名,以PDF格式上传至慕课平台。

12进制计数器评分标准 12进制计数器属于触发器课程的电路设计实验项目,该项目的完成要求具体如下: 1. 12进制计数器不能采用集成计数器芯片完成,只能用触发器设计,否则该项目不能计分。 2. 计数器的实现需要由四个触发器(同步或异步)设计而成,并通过数码管显示当前计数值,否则只能50%计入成绩。 3. 计数器可以设置一个清零键,该内容属于加分项。 4. 报告最后需加入本次实验的心得,字数不限,但切记雷同。 5. 报告请以“班级-学号-姓名”命名,以PDF格式上传至慕课平台。

第7题

用三个下降沿JK触发器及必要的与门设计一个步五进制计数器,其编码如下表所示,然后利用该计数器及3位二进制译码器组成一个周期序列信号发生器,每个周期的序列信号为01101,画出电路图,写出必要的过程。

| Q2 | Q1 | Q0 |

| 0 | 0 | 0 |

| 0 | 0 | 1 |

| 1 | 0 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

第9题

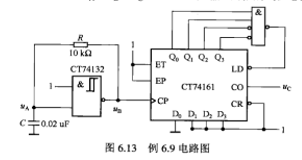

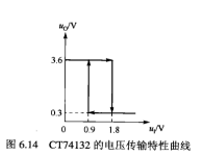

(1)分别指出图6.13中两部分电路组成什么功能的电路(名称).

(2)分析CT74161组成的电路,画出状态转换图.

(3)试画出uA、uB、uC(CO为进位输出端)的对应波形.

第10题

为了保护您的账号安全,请在“上学吧”公众号进行验证,点击“官网服务”-“账号验证”后输入验证码“”完成验证,验证成功后方可继续查看答案!

微信搜一搜

微信搜一搜

上学吧

上学吧

微信搜一搜

微信搜一搜

上学吧

上学吧