题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

三输入或非门的逻辑表达式为()

如搜索结果不匹配,请 联系老师 获取答案

如搜索结果不匹配,请 联系老师 获取答案

更多“三输入或非门的逻辑表达式为()”相关的问题

更多“三输入或非门的逻辑表达式为()”相关的问题

第4题

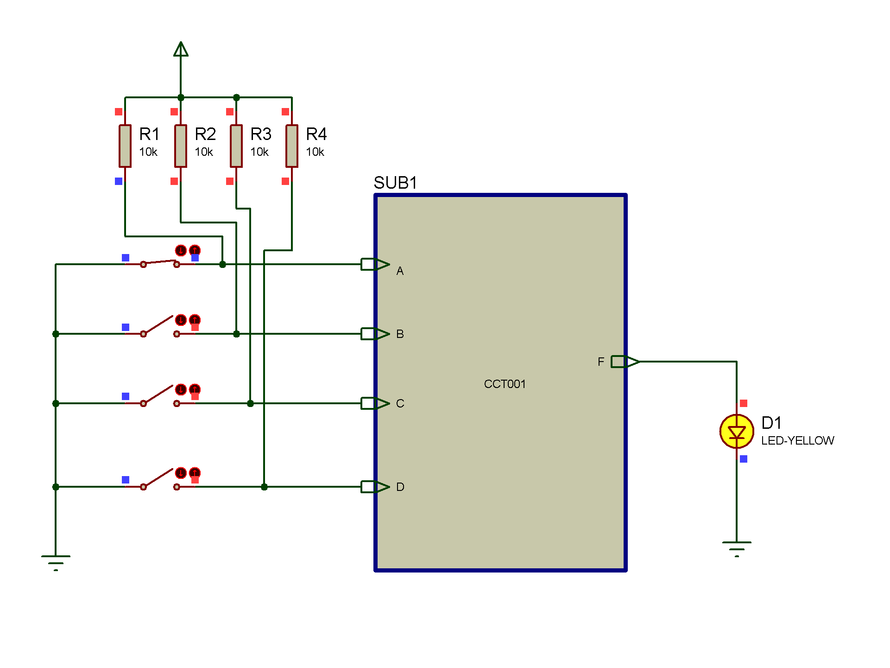

实验二 四人表决器 用“与非”门设计一个表决电路。当四个输入端中有三个或四个为“1”时,输出端才为“1”。 设计步骤:根据题意列出真值表如表2-1所示,再填入卡诺图表2-2中。 表2-1 D A B C Z 表2-2 DA BC 00 01 11 10 00 01 11 10 由卡诺图得出逻辑表达式,并演化成“与非”的形式 表达式 。 根据逻辑表达式画出用“与非门”构成的逻辑电路。 设计效果图如下所示: 用仿真实验验证逻辑功能。 四人表决器属于组合电路中门电路设计的实验项目,该项目的完成要求具体如下: 1. 四人表决的输入终端可以用按钮、逻辑静态终端、开关等替代,但表决结果至少需要有一支发光二极管的输出来显示。 2. 如四人表决电路的逻辑符合要求,但输出有误,只能计入总分的50%。 3. 四人表决器能否表决可以加入使能控制,但不能影响到表决器逻辑的要求,即没有优先权的设计。 4. 四人表决器的实验报告需要包含真值表、表达式、逻辑电路的仿真效果图(可以包含多张)等,请将报告内容完整呈现。 5. 报告最后需加入本次实验的心得,字数不限,但切记雷同。 6. 报告请以“班级-学号-姓名”命名,以PDF格式上传至慕课平台。

用仿真实验验证逻辑功能。 四人表决器属于组合电路中门电路设计的实验项目,该项目的完成要求具体如下: 1. 四人表决的输入终端可以用按钮、逻辑静态终端、开关等替代,但表决结果至少需要有一支发光二极管的输出来显示。 2. 如四人表决电路的逻辑符合要求,但输出有误,只能计入总分的50%。 3. 四人表决器能否表决可以加入使能控制,但不能影响到表决器逻辑的要求,即没有优先权的设计。 4. 四人表决器的实验报告需要包含真值表、表达式、逻辑电路的仿真效果图(可以包含多张)等,请将报告内容完整呈现。 5. 报告最后需加入本次实验的心得,字数不限,但切记雷同。 6. 报告请以“班级-学号-姓名”命名,以PDF格式上传至慕课平台。

第5题

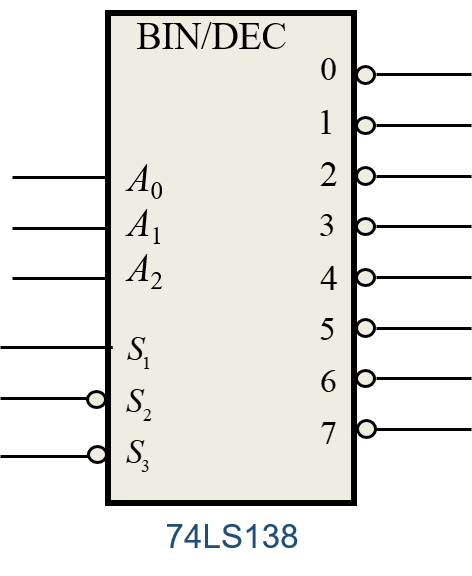

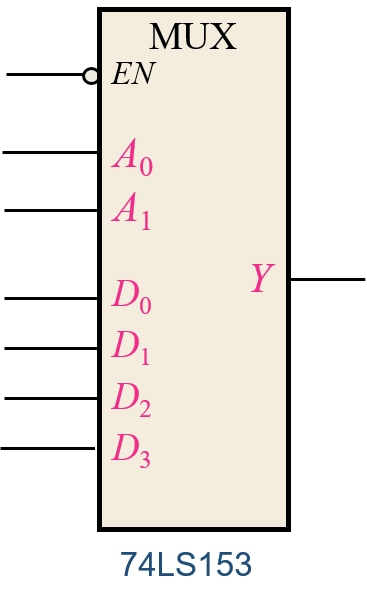

Design a logic circuit to produce a LOW output only if the input, represented by a 3-bit binary number, is between THREE and SIX (Including THREE and SIX). 请设计一个组合逻辑电路满足要求:当输入代表的3位二进制数取值在3和6之间(包含3和6)时输出为低电平。 1)Develop the truth table. 构建真值表 2)Write down the simplified SOP form. 写出最简与或表达式。 3)Implement the circuit use NAND gates only. 只使用“与非”门设计实现该电路。 4)Use a 74LS138 (3-line-to-8-line decoder) and a few gates to implement the circuit. 请使用74LS138(3线-8线译码器)和少量的逻辑门实现该电路。 5)Use a 74LS153 (4-input data selector) and a few gates to implement the circuit. 请使用74LS153(四选一数据选择器)和少量的逻辑门实现该电路。

5)Use a 74LS153 (4-input data selector) and a few gates to implement the circuit. 请使用74LS153(四选一数据选择器)和少量的逻辑门实现该电路。

为了保护您的账号安全,请在“上学吧”公众号进行验证,点击“官网服务”-“账号验证”后输入验证码“”完成验证,验证成功后方可继续查看答案!

微信搜一搜

微信搜一搜

上学吧

上学吧

微信搜一搜

微信搜一搜

上学吧

上学吧