题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

组合逻辑电路的译码功能有()

A.变量译码器

B.显示译码器

C.数码译码器

D.以上都是

如搜索结果不匹配,请 联系老师 获取答案

如搜索结果不匹配,请 联系老师 获取答案

更多“组合逻辑电路的译码功能有()”相关的问题

更多“组合逻辑电路的译码功能有()”相关的问题

第5题

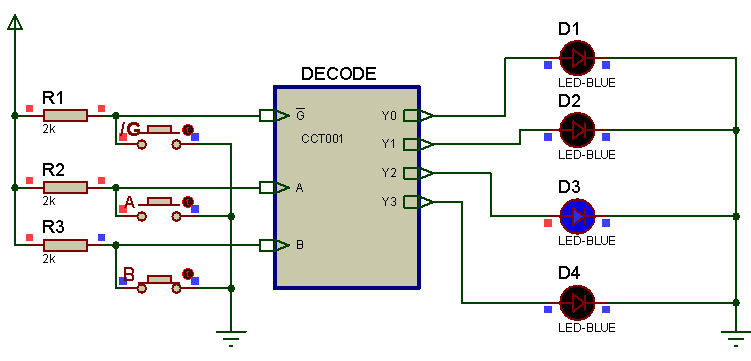

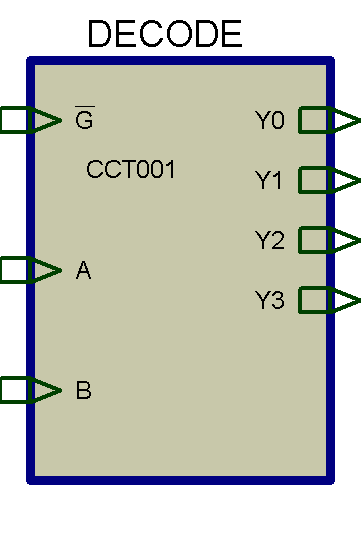

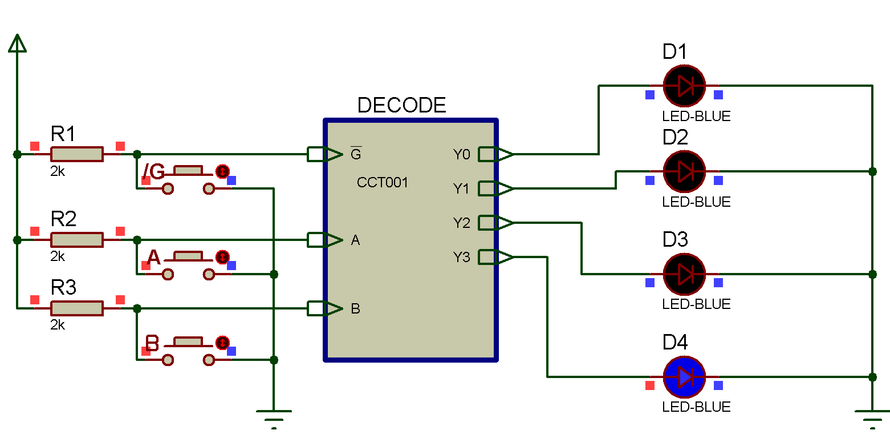

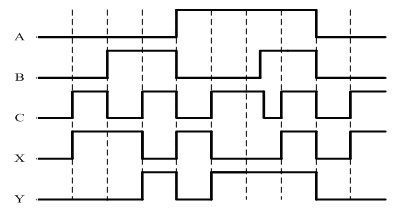

实验一 2-4译码器 对初学者而言,组合电路的设计是我们入门数字电路的第一步,对初学者而言,我们有着丰富的课程案例与大家共享,下面就是一个2-4译码器的设计说明。 1、设计说明 如下图所示,当我们按下A、B或G键时,即启动了译码器的控制端。根据译码器的功能表可知,G键可控制译码器的工作,G按键弹起时:AB=00,D1灯亮;AB=01,D2灯亮;AB=10,D3灯亮;AB=11,D4灯亮。G按键按下时:译码器不工作。 2-4译码器工作原理图 其中DECODE模块的功能是翻译AB的取值,但前提是我们不能使PROTEUS为我们提供的功能芯片---74LS139,而是自制此元件,如上图所示,下面我们给出设计过程。 1.1 设计流程 组合逻辑电路的设计就是在给定逻辑功能及要求的条件下,通过设计方法,得到满足功能要求的逻辑电路。 组合逻辑电路的设计流程如下图所示,首先我们需要绘制2-4译码器的真值表,其次我们需要根据真值表绘制卡诺图并化简,得到逻辑表达式,最终根据表达式绘制逻辑电路并进行仿真。 1.2 设计步骤 1)绘制真值表(参考真值表如下图所示:) 如要求绘制

2-4译码器工作原理图 其中DECODE模块的功能是翻译AB的取值,但前提是我们不能使PROTEUS为我们提供的功能芯片---74LS139,而是自制此元件,如上图所示,下面我们给出设计过程。 1.1 设计流程 组合逻辑电路的设计就是在给定逻辑功能及要求的条件下,通过设计方法,得到满足功能要求的逻辑电路。 组合逻辑电路的设计流程如下图所示,首先我们需要绘制2-4译码器的真值表,其次我们需要根据真值表绘制卡诺图并化简,得到逻辑表达式,最终根据表达式绘制逻辑电路并进行仿真。 1.2 设计步骤 1)绘制真值表(参考真值表如下图所示:) 如要求绘制 的表达式,首先写出其真值表 A B

的表达式,首先写出其真值表 A B 00 01 11 10 0 0 0 0 0 1 1 0 0 0 2)由此写出逻辑表达式:

00 01 11 10 0 0 0 0 0 1 1 0 0 0 2)由此写出逻辑表达式: 3) 据此,完成

3) 据此,完成 、

、 、

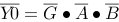

、 的表达式,并完成电路仿真。 2、设计步骤 1)首先,完成核心芯片DECODE模块的设计,实现2-4译码器的一般译码功能,如图所示:

的表达式,并完成电路仿真。 2、设计步骤 1)首先,完成核心芯片DECODE模块的设计,实现2-4译码器的一般译码功能,如图所示: 2 )为DECODE模块加入外围电路,如按键和LED灯,如图所示:

2 )为DECODE模块加入外围电路,如按键和LED灯,如图所示: 在完成上述设计后,你可能需要继续扩展本设计的功能,如3-8译码器及增加相应的使能控制,请努力试试吧!! 2-4译码器属于组合电路中门电路设计的实验项目,该项目的完成要求具体如下: 1. 2-4译码器如使用集成电路74ls139实现,该项目的成绩无效,不计入总成绩。 2. 2-4译码器的输入端如果仅有A、B两个输入,没有芯片的使能控制En,只能计入总分的50%。 3. 译码器的实验报告需要包含真值表、表达式、逻辑电路的仿真效果图(可以包含多张)等,请将报告内容完整呈现。 4. 报告最后需加入本次实验的心得,字数不限,但切记雷同。 5. 报告请以“班级-学号-姓名”命名,以PDF格式上传至慕课平台。

在完成上述设计后,你可能需要继续扩展本设计的功能,如3-8译码器及增加相应的使能控制,请努力试试吧!! 2-4译码器属于组合电路中门电路设计的实验项目,该项目的完成要求具体如下: 1. 2-4译码器如使用集成电路74ls139实现,该项目的成绩无效,不计入总成绩。 2. 2-4译码器的输入端如果仅有A、B两个输入,没有芯片的使能控制En,只能计入总分的50%。 3. 译码器的实验报告需要包含真值表、表达式、逻辑电路的仿真效果图(可以包含多张)等,请将报告内容完整呈现。 4. 报告最后需加入本次实验的心得,字数不限,但切记雷同。 5. 报告请以“班级-学号-姓名”命名,以PDF格式上传至慕课平台。

第7题

A、译码是编码的逆过程

B、译码器的功能是将输入的二进制代码译成对应的输出信号或者另一种形式的代码

C、译码器通常是一个单输入多输出的组合逻辑电路

D、二进制译码器是一种常见的译码器

第8题

A、编码器

B、半加器

C、1位全加器

D、译码器

为了保护您的账号安全,请在“上学吧”公众号进行验证,点击“官网服务”-“账号验证”后输入验证码“”完成验证,验证成功后方可继续查看答案!

微信搜一搜

微信搜一搜

上学吧

上学吧

微信搜一搜

微信搜一搜

上学吧

上学吧