题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

下列对于锁存器和触发器描述正确的是()。

A.锁存器和触发器都是具有存储功能的逻辑电路。

B.每个锁存器或触发器都能存储1位二进制信息。

C.锁存器是对脉冲电平敏感的电路。

D.触发器是对时钟脉冲边沿敏感的电路。

如搜索结果不匹配,请 联系老师 获取答案

如搜索结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

A.锁存器和触发器都是具有存储功能的逻辑电路。

B.每个锁存器或触发器都能存储1位二进制信息。

C.锁存器是对脉冲电平敏感的电路。

D.触发器是对时钟脉冲边沿敏感的电路。

如搜索结果不匹配,请 联系老师 获取答案

如搜索结果不匹配,请 联系老师 获取答案

更多“下列对于锁存器和触发器描述正确的是()。”相关的问题

更多“下列对于锁存器和触发器描述正确的是()。”相关的问题

第1题

A、触发器与锁存器的不同在于触发器增加了一个触发时钟信号。

B、电平触发的触发器只有当CLK变为有效电平是,触发器才能接受输入信号,并按照输入信号将触发器的输出置成相应状态。

C、边沿触发器的次态仅取决于时钟有效边沿到达时输入的逻辑状态。

D、脉冲触发器的次态只考虑CLK下降沿到达时输入的逻辑状态,从而决定次态的变化。

第2题

A、同步触发器的动作特点是在CP=1(高电平期间)的全部时间内,S、R、D、J、K、T等数据输入端的变化可引起触发器状态发生相应变化,因此常被称为电平触发器。

B、边沿触发器的动作特点是触发器的输出状态仅仅取决于CP脉冲上边沿或下边沿到来时的S、R、D、J、K、T等输入状态,在此前或之后,输入状态的变化对输出状态均无影响。

C、基本RS-FF(SR锁存器) 是构成各种高性能触发器的基本单元。

D、RS基本触发器的约束条件是R和S输入不可同时无效。

第3题

A、同步触发器的动作特点是在CP=1(高电平期间)的全部时间内,S、R、D、J、K、T等数据输入端的变化可引起触发器状态发生相应变化,因此常被称为电平触发器。

B、边沿触发器的动作特点是触发器的输出状态仅仅取决于CP脉冲上边沿或下边沿到来时的S、R、D、J、K、T等输入状态,在此前或之后,输入状态的变化对输出状态均无影响。

C、基本RS-FF(SR锁存器) 是构成各种高性能触发器的基本单元。

D、主从类型的触发器一个周期内仅在时钟下降沿有输出,且具有一次变化现象,因而有很强的抗干扰能力。

第4题

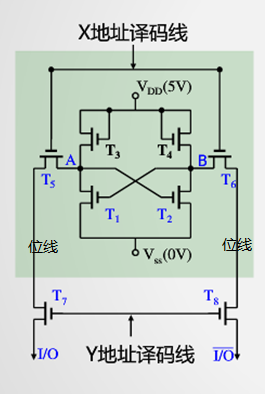

下图所示SRAM存储元中,下列说法正确的是()

下图所示SRAM存储元中,下列说法正确的是()

A、用A点的电平高低表示存储的二进制信息1和0

B、三极管T1和T2呈现互锁关系,B点连接T1的栅极,当B点为低电平(0)时,T1管截止,A点高电平(1)

C、T3和T1管构成一个反相器(非门),其输入为T1的栅极,输出为A点;T4和T2管也构成一个反相器(非门),其输入为T2栅极,输出为B点,因此,该SRAM存储元采用2个非门互锁构成一个触发器电路,其中A点看成是Q端,B点是/Q端

D、上述图所示的存储元存储了2位二进制信息

第5题

A、A. 74LS164是一种 8 位串入并出移位寄存器

B、B.74LS164的移位过程是借助 D 触发器的工作原理实现的

C、C.8 次移位结束后, 74LS164的输出端 Q0 锁存着数据的最高位, Q7 锁存着最低位

D、D.74LS164与 80C51 的串口方式 0 配合可以实现单片机并行输出口的扩展功能

第6题

A、锁存器和触发器都是脉冲电平敏感器件

B、锁存器和触发器都是脉冲边沿敏感器件

C、锁存器是脉冲电平敏感器件,触发器是脉冲边沿敏感器件

D、锁存器是脉冲边沿敏感器件,触发器是脉冲电平敏感器件

为了保护您的账号安全,请在“上学吧”公众号进行验证,点击“官网服务”-“账号验证”后输入验证码“”完成验证,验证成功后方可继续查看答案!

微信搜一搜

微信搜一搜

上学吧

上学吧

微信搜一搜

微信搜一搜

上学吧

上学吧