题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[主观题]

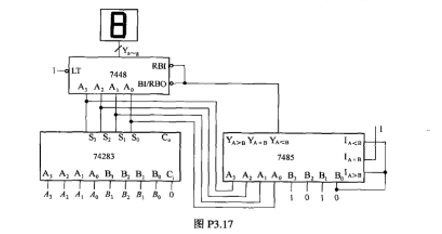

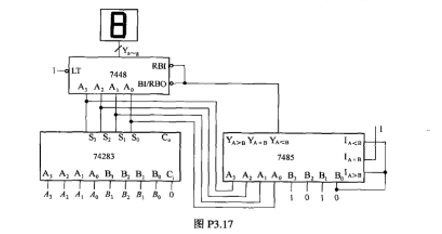

图P3.17电路是由一片4位二进制超前进位全加器74283、比较器7485与七段显示译码电路7448及显示

块LED组成的电路,试分析该电路的逻辑功能.

如搜索结果不匹配,请 联系老师 获取答案

如搜索结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

如搜索结果不匹配,请 联系老师 获取答案

如搜索结果不匹配,请 联系老师 获取答案

更多“图P3.17电路是由一片4位二进制超前进位全加器74283、…”相关的问题

更多“图P3.17电路是由一片4位二进制超前进位全加器74283、…”相关的问题

第1题

B、I/O On Block的端口命名和signals in Node命名不以相同

C、若“a: IN STD_LOGIC_VECTOR(3 Downto 0);”,在转换为symbol时,必须用Orthogonal Bus Tool连接

D、4位串行进位二进制全加器只能用二进制输出来仿真显示

第5题

第6题

第7题

试用1片4位二进制全加器74LS283将2421码转换成8421码。2421码如表所示。

| 2421编码表 | ||||

| 十进制数 | 2421码 | |||

| X | A | B | C | D |

| 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 2 | 0 | 0 | 1 | 0 |

| 3 | 0 | 0 | 1 | 1 |

| 4 | 0 | 1 | 0 | 0 |

| 5 | 1 | 0 | 1 | 1 |

| 6 | 1 | 1 | 0 | 0 |

| 7 | 1 | 1 | 0 | 1 |

| 8 | 1 | 1 | 1 | 0 |

| 9 | 1 | 1 | 1 | 1 |

第9题

为了保护您的账号安全,请在“上学吧”公众号进行验证,点击“官网服务”-“账号验证”后输入验证码“”完成验证,验证成功后方可继续查看答案!

微信搜一搜

微信搜一搜

上学吧

上学吧

微信搜一搜

微信搜一搜

上学吧

上学吧