题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

设有一个4体交叉存储器.单体字长为32位,采用直接映像cache,主存与cache(或CPU)之间的数据传送宽度为32位.问当CPU访存地址为0001H,又cache不命中时,主存与cache传送数据的过程是怎样的?

如搜索结果不匹配,请 联系老师 获取答案

如搜索结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

如搜索结果不匹配,请 联系老师 获取答案

如搜索结果不匹配,请 联系老师 获取答案

更多“设有一个4体交叉存储器.单体字长为32位,采用直接映像cac…”相关的问题

更多“设有一个4体交叉存储器.单体字长为32位,采用直接映像cac…”相关的问题

第2题

每个字有32位。请回答案:

(1)主存地址多少位(按字节编址)。各段如何划分(各需多少位)?

(2)设cache开始为空,CPU从主存单元0,1,…,100依次读出101个字(主存为单体,即非交叉存储器,每次读出一个字),并重复按此次序总共读11次,问命中率是多少?若cache的速度是其不命中时从主存读数速度的5倍,问采用cache与无cache比较速度可提高到多少倍?

第4题

第5题

假设有3种指令和数据合一的cache:

(1)cache1:直接映像,块长为1字,指令命中率为96%,数据命中率为92%。

(2)cache2:直接映像,块长为4字,指令命中率为98%.数据命中率为95%。

(3)cache3;两路组相联映像,块长为4字,指令命中率为98%.数据命中率为96%。

命中时访问一次cache的时间为一个时钟周期。

运行时50%指令存取一个数据。假设主存访问时间为“6加上块的字数”个时钟周期。

求出上述3种情况执行一条指令的平均访存时间.并估计主存可能是一种什么样的结构。

第6题

(按字编址),连续执行10遍,cache的速度为主存的10倍。要求:

(1)计算cache命中率(数据宽度为1字)。有cache与无cache的访问速度比值是多少?

(2)计算cache命中率(数据宽度为双字)。与数据宽度为单字的情况相比,速度提高多少倍?

(3)计算cache的命中率,已知主存储器改为两体交叉存储器。每个体的数据宽度为1个字,主存与CPU之间的数据传送宽度也为1个字。又问总访问时间有无变化?

第7题

时的损失是25个时钟周期.存取数据的不命中率为2%。取指令全部命中。问:

(1)cache采用哈佛结构.如果取指令和存取数据全部命中时的CPI是2.0,那么这台机器实际运行时的CPI是多少?(CPI为运行一条指令的周期数。)

(2)采用指令和数据合一的cache,如果不存在Load/Store指令时的CPI为2.0,那么当存在Load/Store指令时.机器实际运行时的CPI是多少?

第9题

从供选择的答案中,选出正确答案填入。

一般CPU在一条指令执行结束前判断是否有中断请求,若无,则执行下条指令;若有,则按如下步骤进行中断处理。步骤a,关中断,然后将断点(PC内容)和程序状态字等现场保存,并转入中断处理程序。步骤b,判断中断源,根据中断源进入处理相应中断的处理程序。步骤c.先做好交换新旧中断屏蔽码等准备工作后即执行开中断,然后进入具体的中断服务程序执行中断服务。步骤d,先关中断,然后恢复现场。步骤e.先执行开中断,然后立即执行中断返回。

步骤a由A实现。若采用向量中断方式.则不必执行步骤b.步骤c中开中断的目的是B。由于设置了C,故可在多重中断发生时改变中断响应顺序。步骤e的开中断是由D实现的。

供选择的答案:

A:①程序:②中断隐指令(硬件)。.

B:①使原来的屏蔽码不起作用;②便于高级的中断请求得以及时处理。

C:①新的屏蔽码;②开中断。

D;①程序;②硬件。

第10题

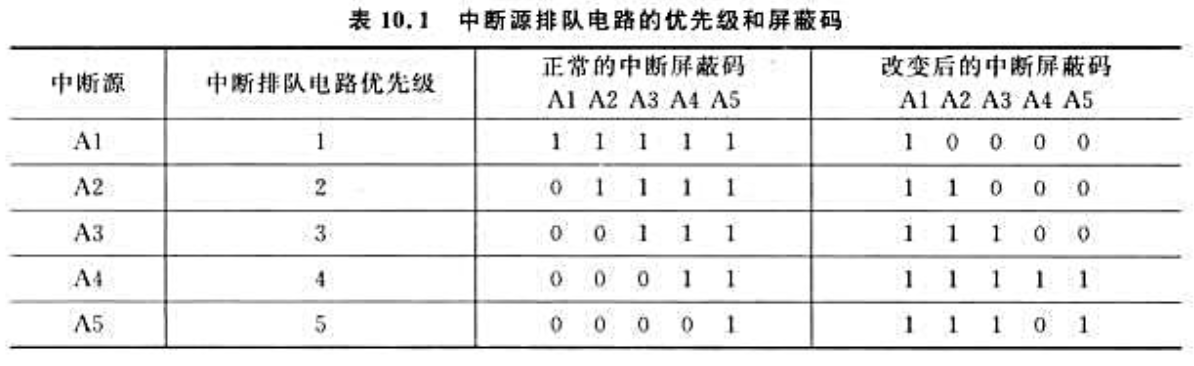

级中断源在响应中断后正常设置的中断屏蔽码和改变后的中断屏蔽码如表10.1所示,其中“1”表示该中断源被屏蔽,“0”表示该中断源不被屏蔽。

如果5个中断源同时提出中断请求,请回答:

如果5个中断源同时提出中断请求,请回答:

(1)在中断源提出中断申请之前,中断屏蔽码应该是何值?

(2)仅使用正常的中断屏蔽码,处理机响应各个中断请求的先后次序是什么?完成各个中断请求的先后次序是什么?

(3)当使用改变后的中断屏蔽码时.处理机响应各个中断请求的先后次序是什么?完成各个中断请求的先后次序是什么?请画出程序运行过程的示意图。

为了保护您的账号安全,请在“上学吧”公众号进行验证,点击“官网服务”-“账号验证”后输入验证码“”完成验证,验证成功后方可继续查看答案!

微信搜一搜

微信搜一搜

上学吧

上学吧

微信搜一搜

微信搜一搜

上学吧

上学吧